2020年2月6日,美光科技宣布交付全球首款量产的低功耗DDR5 DRAM 芯片,随后,三星S20系列和小米10系列手机先后发布,全新的LPDDR5内存成为两家的共同卖点之一,这也预示着DDR5的时代即将到来。今天我们就来聊一聊DDR5的发展过程,设计难题以及如何通过仿真来应对DDR5设计挑战。

01. DDR技术的发展历程

02. DDR5的出现,带来了哪些设计挑战?

03. 如何通过仿真及建模中的创新克服DDR5技术挑战

04. DDR5仿真解决方案

05. DDR5仿真实例

01DDR技术的发展历程

在计算机和移动设备中,DDR是数据的缓冲区,CPU所需访问与处理的数据几乎都会经过这里。与此同时,除了暂存CPU运算数据,DDR还需要承担与外部储存器交互数据的使命。随着CPU处理能力的不断提高,对DDR的速度和容量的要求也在不断地提升。

从DDR的发展图中可以看到,DDR的传输速率在成倍提升,而其迭代速度也在不断加快。

如今,占据着主流市场的是从2014年底开始上市的DDR4。较低的工作电压以及最高可达4266MT/s的传输速率,使其达到前代DDR3三倍速率的同时,拥有更低的功耗。

但是,随着CPU的核数不断增多,内存的性能又将成为新的瓶颈。因此JEDEC协会早在2017年就开始和各大SDRAM厂商协作,着手起草DDR5标准,DDR5技术规范草案和LPDDR5的更新标准都已公布,不过至今还未推出正式版本。

目前而言,DDR5的最高速率预计可以达到8.4GT/s,是DDR4的两倍。同时,工作电压也从1.2V降低到了1.1V,这也意味着DDR5在性能提高的同时,进一步降低了功耗。

02 DDR5的出现,带来了哪些设计挑战?

DDR5的速率最高超过8.4GT/s,达到了前代DDR4最高速率的两倍。更高的速率,带来出色性能的同时,不可避免的提升了设计的困难。

挑战1:串扰(Crosstalk)

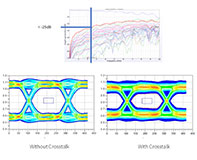

DDR信号较多,走线较为密集,随着信号速率的增加,传输线之间的串扰也会随之增加。此外,DDR颗粒的引脚布局,往往多个信号附近只有一个GND引脚,这就使得这些信号需要共用同一个返回路径,更加增加了相互干扰的风险。

在图中不难发现,单一传输线之间的串扰都在-25dB以下,这个是相对不错的结果。然而,即使如此,在观察眼图时可以发现,串扰较为严重地减小了眼图地张开程度。这就意味着,单独从单一传输线的串扰角度上,并不能确切的得到串扰真实造成的影响,这给设计过程中,带来了困难。

挑战2:抖动(Jitter)

除了串扰外,抖动也是不能被忽视的问题。

在上图可以看到,仅仅考虑随机抖动后,眼图的时间裕量就减小47%(27ps)。这意味着,如果忽视了抖动的影响,很容易对设计的质量的评估过优,最后造成实际产品的失败。

挑战3:码间干扰(ISI)及均衡(Equation)

由于传输线的频率选择特性,频率越高,传输线的插入损耗也会随之增加,信号的衰减和码间干扰的现象也会更加严重。

图中传输线在1.2GHz时插损约在-10dB左右,而上升到3.2GHz后,插损达到了-30dB。对比眼图可以发现,6.4Gbps时,由于ISI和衰减,眼图已经完全闭合。

为此,DDR5引入了可调增益以及判决反馈均衡器(DFE),减小ISI对相邻bit的影响,用以改善眼图闭合的情况。

与SERDES中使用的DFE不同的是,在SERDES中,DFE的时钟信息可以由信号本身通过时钟恢复获得。而在DDR5中,由于DQ信号是通过DQS信号触发的,所以需要将DQS作为时钟信号,加入到DFE中去。最后形成的是双输入,单输出的DFE。

挑战4:测试方法

低误码率:

在DDR5的协议草案中,要求在测试时系统的误码率要在10e-16以下,及最少需要5.3e9个UI,才能保证99.5%的置信水平。无论是在测试,还是仿真中,如此多的bit数都需要花费大量的时间。

虚拟探针:

由于DDR5引入了均衡器,所以最终的接受信号是经过均衡后的得到的结果。但是在测试时,往往只能直接测量到芯片BGA封装上的信号波形。所以,需要通过软件仿真或推测模拟出封装以及均衡器的影响,再通过一个虚拟探针,获得最后的波形进行分析。

Loop-back模式:

在DDR5芯片中,有一个RCD接口,可以将最后经过均衡处理的数据输出。测试时可以利用这个接口,将输入的信号与最后RCD 接口输出的信号进行对比,获得整个系统的误码率。

03如何通过仿真及建模中的创新克服DDR5技术挑战?

相对于测试而言,仿真能在较前期对设计进行评估,帮助工程师及时优化设计。这对减少产品风险以及因迭代优化产生的时间和成本有很大的帮助。同时,由于仿真允许在电路的任意节点检测信号质量,也不存在DDR5测试过程中无法直接测量到均衡后信号的问题。

通道仿真

正如上文提到的,DDR5协议草案中,有低误码率的要求。如果使用传统的瞬态算法,就需要将5.3e9个bit逐一卷积计算,这将花费大量的时间,与仿真尽早,快速评估设计的初衷不符,也往往很难实现。 为此,在DDR5的仿真中,就必须使用类似于广泛应用于SERDES仿真当中的通道仿真技术。传统适用于SERDES的通道仿真分成两种模式,其一是逐bit模式(bit-by-bit),这种方式会得到单个bit的阶跃响应,在通过仿真器根据输入的bit序列,将对应的阶跃响应进行叠加。而另一种则是统计模式(statistical),即整个系统的响应,包括抖动,串扰,均衡等,都是基于单个bit的阶跃响应,根据概率密度分布结果,经过数据后处理获得。由于DDR信号多为单端信号,与SERDES的差分信号不同。因此,应用在DDR上的通道仿真技术,还需要有一些改动。首先是通道仿真技术所需要的阶跃响应。差分信号的上升沿与下降沿是对称的,因此只需要获得单一的阶跃响应进行通道仿真。而对于单端信号而言,上升时间和下降时间不再相同,这就意味着需要同时获得上升和下降两个阶跃响应,同时,仿真器需要在信号上升和下降时使用对应阶跃响应进行计算。

其次是时钟问题。SERDES信号往往是通过时钟恢复电路(CDR),从信号本身恢复出时钟信号。而DDR则不同,DQ信号由DQS信号触发。这就需要仿真器具有时钟触发的功能。否则,如果依旧使用DQ信号本身进行时钟恢复的话,会造成时域的偏移。下图中,红色部分为DQ时钟恢复后结果,蓝色为DQ由DQS触发后的结果。可以看到,两个结果在时间上存在一个偏移量。

最后是关于DDR的write-leveling功能。Write-leveling允许设备调整ClK信号与DQS信号之间的时间差。如果仿真器不能实现这个功能,会带来不必要的调整。

在这里需要注意的是,如果需要使用Rx端DFE的自适应模式,必须在bit-by-bit模式下进行仿真。而statistical模式下,只支持固定抽头系数的仿真。

在ADS2015中,基于通道仿真技术改进而来的DDR BUS仿真器就已经被应用到DDR仿真中,并在更新中不断完善,以应对DDR5仿真带来的挑战。

IBIS-AMI模型

在前代的DDR仿真中,IBIS模型已经得到了广泛的应用。而DDR5与之前协议的一个很大的差别,就是需要在Rx使用可调增益和DFE的均衡方式对接收到的数据进行处理。这就给了IBIS-AMI模型发挥的舞台。

IBIS-AMI模型不仅可以在保护IP的前提下满足各种均衡的需要,而且作为一个通用模型,能在各种工具中进行使用。

当然,虽然IBIS-AMI模型已经在SERDES信号中被广泛使用。但是这毕竟是第一次应用在单端信号中,有一些部分需要改进。

首先是直流偏置的问题。差分信号不存在直流偏置,因此在使用单端的IBIS-AMI模型进行均衡计算时,直流偏置必须可以通过算法解决。

第二点便是DQS提供时钟信号的问题了。在前文中介绍过,DDR5的DFE均衡需要DQS提供时钟信号。这就意味着,DDR5的IBIS-AMI模型,不仅需要有DQ信号的输入端,还需要DQS信号的输入,才能恢复出符合要求的信号。

在ADS2020 Update1中,Memory Designer已经支持IBIS-AMI模型在DDR5仿真中的应用,可以使用IBIS-AMI模型对于DDR5的均衡效果进行仿真。

针对之前提到的所有挑战与创新,如上表所示,Keysight Pathwave平台的SystemVue,ADS Memory Designer以及ADS SIPro提供了完整的解决方案。(以下案例中使用了Intel提供的IBIS-AMI模型)

SystemVue

SystemVue是一款被广泛应用于AMI建模的软件。用户可以使用SystemVue中包含的通用算法模块,快速的构建所需的均衡模型,同时完成AMI模型的编译和仿真验证。将原来可能需要花费一整年的AMI建模周期缩短到原有的四分之一。

首先,针对直流偏置,在BIRD197.7中,引入了一个新的参数DC_Offset来表示直流偏置。该参数作为一个固定值由EDA软件定义。在处理波形时,就将DQ信号的直流分量进行抵消,从而保证进入Rx均衡算法中的是中心电压为0V的波形。

在另一方面,针对DQ信号的DFE需要以DQS作为时钟的问题,Keysight与Intel协作,一同提出了一个新的双输入单输出的时域波形处理(getwave)函数long AMI_GetWave2()。使用该函数处理时域波形时,可以同时考虑DQ和DQS的输入。保证在DFE均衡的时候,能够从DQS中获取时钟信号进行计算。

Keysight Pathwave SystemVue可以提供完整的DDR5 AMI 建模解决方案,同时也是唯一一个能够提供long AMI_GetWave2() 以支持DQ和DQS双输入的建模工具。

ADS SIPro

ADS SIPro是一款专用于PCB仿真的EM仿真工具。针对引脚众多的DDR信号,SIPro中内置了DDR设置向导,可以帮助用户快速进行DDR仿真设置。

用户只需要选择控制器及内存模块,相应的网络就会由软件自动筛选提取。用户勾选需要仿真的网络名后,对应的仿真设置便会自动生成。整个过程只需要一分钟左右的时间。

此外,SIPro可以快速准确的提取PCB信号的S参数,可信频率高达40GHz。对于DDR中常见的共用返回路径的情况,SIPro通过算法识别过孔区域,使用三维电磁场算法FEM,精确提取由此产生的串扰,保证仿真精度。

Memory Designer

ADS Memory Designer是ADS中专门针对DDR仿真定制的组件。其目的就是减小DDR仿真的复杂度,同时保证DDR仿真的效率和精度。

在Memory Designer中,只需要一张原理图便可以分别进行通道和瞬态仿真。而由于总线形式的使用,则将传统设置方法所需的数小时,缩减至数分钟,同时也减小了设置错误的风险。

此外,Memory Designer中的DDR BUS仿真器,可以根据信号的上升与下降,使用对应的阶跃响应,获得正确的波形。如下图所示,DDR BUS仿真器在上升沿与下降沿不对称的情况下,有很高的精确度。

另一方面,基于Keysight成熟的通道仿真算法,DDR BUS仿真器可以根据AMI模型中的均衡算法,对信号进行均衡,同时可以准确预测在低误码率情况下的抖动对信号的影响。在下图中也可以发现,当DQ与DQS存在时间差时,会造成眼图的偏移。

05 ADS DDR5仿真实例

图中显示了在ADS Memory Designer环境中DDR5基本的仿真结构,所有信号以总线形式连接,设置过程只需要短短几分钟。其中控制器和内存模块都使用了IBIS-AMI模型,并且允许对AMI模型中的参数进行编辑。

图中显示了DDR5在ADS Memory Designer 中的仿真结果。可以发现,经过AMI模型中均衡算法处理的DQ信号,眼图张开程度明显增加。

以上介绍了DDR5带来的挑战,以及为了应对这些挑战,Keysight Pathwave做出的创新与应对。

- 关键词:DDR5 仿真 芯片

- 浏览量:1686

- 来 源:是德科技KEYSIGHT

- 编辑:清风

- 声明:凡本网注明" 来源:仪商网"的所有作品,版权均属于仪商网,未经本网授权不得转载、摘编使用。

经本网授权使用,并注明"来源:仪商网"。违反上述声明者,本网将追究其相关法律责任。

本网转载并注明自其它来源的作品,归原版权所有人所有。目的在于传递更多信息,并不代表本网赞同其观点或证实其内容的真实性,不承担此类作品侵权行为的直接责任及连带责任。如有作品的内容、版权以及其它问题的,请在作品发表之日起一周内与本网联系,否则视为放弃相关权利。

本网转载自其它媒体或授权刊载,如有作品内容、版权以及其它问题的,请联系我们。相关合作、投稿、转载授权等事宜,请联系本网。

QQ:2268148259、3050252122。 -

-

新一代内存DDR5带来了哪些改变?技术分析|2021-05-20

新一代内存DDR5带来了哪些改变?技术分析|2021-05-20 -

如何解决DDR内存系统测试难题?技术分析|2020-11-24

如何解决DDR内存系统测试难题?技术分析|2020-11-24 -

DDR5时代已经来临!仿真帮你应对新的设计挑战技术分析|2020-03-10

DDR5时代已经来临!仿真帮你应对新的设计挑战技术分析|2020-03-10 -

电流互感器技术大揭秘:从传统到前沿,丈量电力新精度技术分析|2025-07-02

电流互感器技术大揭秘:从传统到前沿,丈量电力新精度技术分析|2025-07-02 -

信号发生器:核心技术与前沿趋势深度剖析技术分析|2025-06-12

信号发生器:核心技术与前沿趋势深度剖析技术分析|2025-06-12 -

基于柔性探头的电容放电瞬态电流分析技术分析|2025-06-09

基于柔性探头的电容放电瞬态电流分析技术分析|2025-06-09 -

《计量测试关键技术创新攻关行动方案》技术分析|2025-05-30

《计量测试关键技术创新攻关行动方案》技术分析|2025-05-30 -

这些动物,天生拥有"红外热成像"技能!技术分析|2025-05-30

这些动物,天生拥有"红外热成像"技能!技术分析|2025-05-30 -

FLIR MIX新技术开启多光谱红外成像新纪元,让视图分析简单高效!技术分析|2025-05-07

FLIR MIX新技术开启多光谱红外成像新纪元,让视图分析简单高效!技术分析|2025-05-07 -

示波器波形捕获率:定义、原理与技术实现全解析技术分析|2025-04-28

示波器波形捕获率:定义、原理与技术实现全解析技术分析|2025-04-28 -

电网波动测试为何如此重要?技术分析|2025-04-03

电网波动测试为何如此重要?技术分析|2025-04-03 -

技术分享 | 真空炉测温与控温技术分析:热电偶与红外测温仪的选择技术分析|2025-02-24

技术分享 | 真空炉测温与控温技术分析:热电偶与红外测温仪的选择技术分析|2025-02-24 -

【美瑞克小课堂】电弧和闪络的区别技术分析|2025-02-15

【美瑞克小课堂】电弧和闪络的区别技术分析|2025-02-15