CDR的背景

随着5G/数据中心的高速发展,光传输向着更高速率、更低延时演进,这就要求对应的光模块经过传输后尽量减小失真,以便在接收端将信号完整地再生出来。从10G长距到25G,再到50G/200G/400G PMA4,由于光纤传输链路线性/非线性效应,因此需要引入时钟数据恢复技术(CDR:Clock Data Recovery)。

CDR的原理

时钟恢复(CDR)的原理:

首先,利用本地产生的多相位时钟对数据多次采样,判断数据比特的边沿,并通过PLL将时钟边沿与其对齐,从而实现与数据同频率、同相位时钟的恢复。

其次,利用已同步时钟的最优相位对输入数据采样,使其实现最高的输入信噪比,并把采样结果作为已恢复数据输出。

时钟是数字通信的基础,在设备发射端,数据是根据时钟的节拍,一拍一拍拍出来的。同样在接收端,数据也是根据时钟的边沿(上升沿/下降沿)来采样获得的。

图1

如果没有时钟做标定,一连长串的数据没有意义,如上图,是101,还是110011?如何解决这个问题呢?

1)随路时钟(trigger), 不需要额外的时钟恢复,但是需要多一路时钟信道。

图2

2)时钟恢复,需要接收端具备时钟恢复的能力。那么如何从串行数据中提取时钟呢?

CDR结构组成

CDR核心--锁相环(PLL:Phase Lock Loop)

数据经过CDR恢复的时钟再生以后,变成理想信号,这个比较容易理解。重点就是这个时钟是怎么恢复出来的,这个也就是CDR的核心部分,即锁相环PLL。

图3

锁相环有3个部分组成:鉴相器、低通滤波器、压控振荡器(VCO)。

鉴相器PD(Phase Detector/phase comparator)

图4 PD/CP示意图

经过鉴相器以后,频差(或者相差)再经过低通滤波器的积分,就以电压的形式控制VCO的输出频率。VCO(压控振荡器)是一个电压控制频率输出的器件。实质上这个过程就是一个电压反馈回路:

1)当时钟频率低于输入信号频率时,电压越来越大(PWM占空比增大,高电平占比增多),VCO输出频率提高,时钟加快;

2)当时钟频率高于输入信号时候,电压越来越小(PWM占空比减小,低电平占比增多),VCO输出频率减小,时钟减慢;

通过以上两个过程,实现动态平衡,最终VCO输出的频率锁定(等于)输入信号的频率。

图5 频率相位锁定

上图DATA IN是理想的010101电平。但是实际上数据输入可能是11001100011100001111,有长连0,长连1的。那么此时该如何处理呢?

对于数字逻辑来说频率最快的是0101,如果出现了长连0或者长连1以后,我们可以理解为此刻信号的频率变低了:

经过鉴相后PD OUT有长高/长低电平,此时VCO频率会降低,时钟就会减慢;

时钟减慢后,此时PD OUT又出现了高电平,又需要将时钟变快,如此反复调节完成动态的平衡,最终时钟锁定。

我们知道锁相环里面的低通滤波器是个积分器,上面出现的有限的连0和连1,不会改变VCO的电压,因为积分器需要一定的时间才能引起VCO上电压的变化。如果连续的连0或者连1太多,将会导致VCO上的电压发生改变,就会引起失锁。

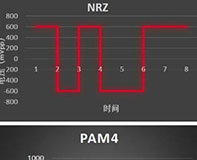

PAM4的CDR

以上是基于NRZ 的CDR的介绍,到了PAM4以后,时钟数据又怎么恢复的呢?PAM4 CDR相对于NRZ信号的CDR而言,其设计难度增大。但是其基本原理差不多,都是依据PLL实现时钟锁定。

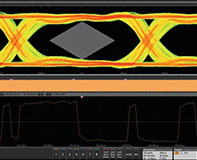

图6 PAM4 CDR结构

PAM4的时钟提取

1)串并转换,将25 GBaud的PAM4信号转成4路并行的6.25 GBaud PAM4信号,并行化的好处是降低每路的波特率(速率),让PLL更容易捕捉频率和相位,也会获得更好的抖动性能。

2)PD的核心部分是其前端电路 (PD-FE),它由并行的3 条数据通路和1条边沿通路构成,而每条通路均包含了1个判决器。PD-FE中除3位判决器之外通过一种新型的积分器,用来实现前述相邻数据的积分,并据此给出调节时钟相位的超前(DN) /滞后(UP)信号,进而控制锁相环路中的CP对环路滤波器(LPF)充放电流,闭环调节时钟相位。

CDR的测试应用

1、实际测试中为什么需要CDR?

通常测试光模块眼图或者BER时,需要一个时钟和被测光信号同步,才能进行眼图或者BER测试。前面介绍了CDR的基本原理,那么实际应用中为什么需要CDR呢?

标准定义:

Ethernet IEEE 802.3,Fibre Channel, 以及OIF-CEI协议里规定,测试抖动,眼高/眼宽必须使用时钟恢复;

测试场景需要:

针对NRZ测试方面,如果待测件环境无法提供时钟输出,此时则需要CDR从信号中来提取时钟;针对PAM4测试方面,特别是400G的光模块,成为业界关注的重点。当前400G主流的光模块,不论是400G-FR8/LR8还是400G-FR4/DR4的实现方式其电口侧都是8路53 Gbps PAM4信号。

对于400G-SR8/FR8/LR8等模块来说,光模块内部只是做CDR(时钟恢复)以及电/光或光/电转换,因此光口侧与电口侧一样,也是8路53 Gbps PAM4信号。此种情况测试光眼图BER,可以采用电口侧的时钟作为示波器的trigger(此时时钟和光信号是同步的),也可以CDR来提取时钟。

但是对于400G-DR4/FR4/LR4等模块来说,光模块内部还有Gearbox DSP芯片做了retime处理,把两路电口输入复用成一路信号再调制到光上,因此光口侧的速率是电口侧速率的2倍,即4路106 Gbps PAM4信号。此时电口侧和光口侧的时钟不同步,我们则必须要用一个外部的CDR来提取时钟,以便trigger和光信号同步,才能测试106 Gbps的光眼图。

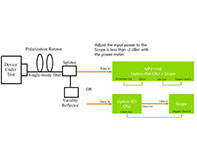

图7 53G CR

2、CDR对测试的影响

a)Loop Bandwidth

PLL带宽选择越宽,信号越容易锁定,容忍信号的变化范围也大,但是输出的抖动也大;PLL带宽越窄,输出抖动越小,但是信号有变化时容易失锁。

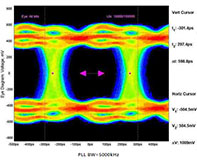

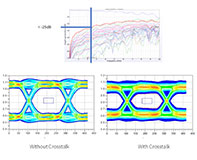

图8 不同BW的CR输出

b)输出抖动

理想情况下PLL能及时追踪到数据跳变沿(即锁住相位),输出的时钟与输入数据同相,即抖动为零。实际情况中,当连续边沿的抖动变化太快时,PLL不能及时追踪到边沿的变化,于是恢复的时钟和数据边沿存在抖动,它的抖动传递函数(Jitter Transfer Function)的频响为高通滤波特性。这个抖动最终会传递到光眼图上,影响mask margin,TDEC/TDECQ等指标。TDECQ的测试中,对CDR的要求是环路带宽4MHz, slope 20dB/dec。

图9 抖动传递

总结

随着光通信的不断发展,PAM4技术的引入、数字芯片在光模块中的使用,以及后续的COBO/CPO封装的应用,在各种测试场景里,都需要使用到CDR以确保符合规范并进行准确的测试。

引用资料: 《面向5G通信的高速PAM4 信号时钟与数据恢复技术》

- 关键词:时钟恢复 CDR 通信测试

- 浏览量:33936

- 来 源:安立通讯

- 编辑:清风

- 声明:凡本网注明" 来源:仪商网"的所有作品,版权均属于仪商网,未经本网授权不得转载、摘编使用。

经本网授权使用,并注明"来源:仪商网"。违反上述声明者,本网将追究其相关法律责任。

本网转载并注明自其它来源的作品,归原版权所有人所有。目的在于传递更多信息,并不代表本网赞同其观点或证实其内容的真实性,不承担此类作品侵权行为的直接责任及连带责任。如有作品的内容、版权以及其它问题的,请在作品发表之日起一周内与本网联系,否则视为放弃相关权利。

本网转载自其它媒体或授权刊载,如有作品内容、版权以及其它问题的,请联系我们。相关合作、投稿、转载授权等事宜,请联系本网。

QQ:2268148259、3050252122。 -

-

光模块RINxOMA测试简析技术分析|2022-05-17

光模块RINxOMA测试简析技术分析|2022-05-17 -

PAM4光眼图测试中的时钟恢复技术分析|2021-05-17

PAM4光眼图测试中的时钟恢复技术分析|2021-05-17 -

安立误码仪MP1900A独特的误码分析功能技术分析|2020-11-11

安立误码仪MP1900A独特的误码分析功能技术分析|2020-11-11 -

专治抖动!查找和诊断功率完整性问题导致的抖动技术分析|2020-10-13

专治抖动!查找和诊断功率完整性问题导致的抖动技术分析|2020-10-13 -

深入浅出聊聊时钟恢复CDR技术分析|2020-09-28

深入浅出聊聊时钟恢复CDR技术分析|2020-09-28 -

如何进行时钟恢复长0和长1接收容限的测试技术分析|2020-06-23

如何进行时钟恢复长0和长1接收容限的测试技术分析|2020-06-23 -

3分钟玩转示波器的眼图与抖动分析技术分析|2020-05-29

3分钟玩转示波器的眼图与抖动分析技术分析|2020-05-29 -

技术分析:传输线长度对高速信号误码测试的影响技术分析|2020-05-28

技术分析:传输线长度对高速信号误码测试的影响技术分析|2020-05-28 -

DDR5时代已经来临!仿真帮你应对新的设计挑战技术分析|2020-03-10

DDR5时代已经来临!仿真帮你应对新的设计挑战技术分析|2020-03-10 -

解析UV LED如何进行光通信?LED行业|2016-01-07

解析UV LED如何进行光通信?LED行业|2016-01-07