引言

看过《三体》的朋友们,一定对震撼的人列计算机有所印象:冯 · 诺依曼让秦始皇安排三千万个士兵组成的人列计算器,通过士兵举黑白旗显现的信号代替了二进制进行运算;通过骑马的轻转兵在整个系统间传递信息代替了总线进行数据传输;并利用三百万名文化程度较高的学者每个人手中的记录本和笔,负责记录运算结果代替了存储器。这就形成了控制器和运算单元、总线以及存储器的概念。

不知道读者在阅读这一段的时候是否有一个疑问,为什么不能有一个聪明的士兵既能做运算又能记录运算结果,实现“存算一体化”, 从而降低包括数据搬移在内所带来的巨大开销?

应用背景

正像三体中描述的人列计算机,目前大多数芯片系统采用的是冯·诺依曼架构,处理器和存储器由总线连接,数据需在二者之间来回搬运。但随着大数据和人工智能时代的到来,传统的计算存储分离的硬件架构不得不面对冯·诺伊曼瓶颈。数据搬移带来的能耗开销使得存算分离的传统架构难以满足低功耗的系统设计需求。在一些神经网络硬件加速器中,核心的数据处理消耗的能量只有不到10%,除此之外与数据传输相关的能耗才是制约整个系统能效的关键问题。

如图1所示,为了打破冯·诺依曼瓶颈的束缚,存算一体的计算架构开始兴起,逐渐从近存储的计算范式到以存储为中心的计算范式演进。近年来,半导体制造工艺的发展和人工智能领域的崛起,为存算一体技术提供了全新的制造平台和产业驱动力。除了在人工智能及深度学习领域的广泛应用,存算一体架构同样适用于未来主流的感存算一体芯片和类脑芯片。

图1 冯·诺依曼架构和存算一体架构示意图

存算一体芯片旨在把传统以计算为中心的架构转变为以数据为中心的架构,直接利用存储器进行数据处理。近年来非易失性存储器技术的发展,为存算一体芯片的高效实施带来了新的曙光。

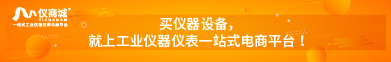

我国在这方面的研究也取得了一系列的创新成果,例如2016年北京大学康晋峰教授团队提出以阻变器件替代传统的CMOS器件来实现逻辑计算。构建了基于触发电平时序的逻辑计算类型,得到可以实时逻辑重构的计算、存储一体化并行处理硬件架构。2021年,中国科学院微电子研究所的刘明团队设计了超薄铁电隧道结进行时间数据学习的节能而稳健的储层计算系统,该系统以高的能效、处理速度 和识别精度完成数字序列分类。2021年复旦大学周鹏团队研究出二维铁电沟道晶体管(2D FeCTs),该FeCTs兼具优异的非易失存储功能和神经拟态能力。如图2所示,该器件成功实现了对鸢尾花图像的高精度分类。2022年国防科技大学电子科学学院徐晖教授课题组与复旦大学芯片与系统前沿技术研究院刘琦教授课题组合作,首次实现了一种与CMOS工艺完全兼容的氧化铪基反铁电神经元。该反铁电晶体管能模拟生物神经元积分发射特性,且由于其自发的去极化现象避免了大尺寸电容和复位电路的使用,有效提高了神经形态计算芯片集成度。如图3所示构建的784×400×10双层神经网络,手写体识别率高达96.8%,对促进新原理器件在图像、语音等智能化处理场景的应用具有重要意义。2022年,华东师范大学段纯刚教授团队利用铁电突触晶体管神经网络成功实现了联想学习,达到输入了不完整的像素,也可以从硬件成功输出完整像素的图像识别功能。

图3 双层全铁电SNN示意图及基于FeFET突触和AFeFET神经元网络的硬件

测试方案介绍

存算一体芯片旨在把传统以计算为中心的架构转变为以数据为中心的架构,直接利用存储器进行数据处理。存算一体芯片在当代研究的最新神经元网络中扮演高速存储计算单元,其主要技术路线有通过阻变,容变等方式实现。存算一体芯片在当代研究的最新神经元网络中扮演高速存储计算单元。在研发阶段,目前很多机理的存算一体芯片都需要反复测试验证迭代,必须需要有一套合适的测试系统加速这一过程。在这个过程中,如何快速将单个单元的测量扩展到阵列形式的测量,是实验室必须要解决的一个测量难题。

测试需求

◾ 单个单元的性能测试

◾ 可扩展的多单元性能测试

◾ 存算一体阵列芯片的测试

◾ 模拟应用的测试方法

阵列测试流程

1. 对阵列中的行列每个单元通过施加脉冲,进行预设置,记录I-V特性。

2. 预设置整体阵列后,再次对每个行列单元按序列施加脉冲,记录充放电情况及极化反转等特性。

3. 不同的序列脉冲施加,测试不同行列激励下的不同反应。

4. 测试过程中需要反复施加脉冲,并且同步测量I-V特性并需要友好方便的编程方式满足不同的激励测试需求

基于以上的测试需求和难点,上海众执芯信息科技有限公司基于NI平台推出存算一体化测试系统(ZoX MRAM Test System),可扩展至1024*1024阵列规模或更大规模;提供高精度的I-V测试与不同的脉冲测试方案;并可根据客户的器件特性,进行方案定制及实现。

图4 NI测试平台

NI拥有丰富的SMU与Matrix产品,可以相互组合,应对不同规模的存算一体阵列需求,结合PXIe的高性能同步与LabVIEW的快速开发能力,配合ZOX针对存算一体芯片开发的测试软件,可支持客户进行存算一体相关课题的研究与验证。

近日,NI与华东师范大学段纯刚、田博博教授团队合作开发了一套存算一体化芯片的验证系统。通过软件控制摄像头实时采集图案,并转化为数字图像;由NI多通道设备向芯片(铁电电容器阵列)写入该图像信息,然后利用铁电电容器的动力学特性对图像进行实时处理,达到提取动态信息的目的。合作搭建的系统很好的验证了该芯片可实现图像存储和动态识别的功能。

- 浏览量:21646

- 来 源:众执芯信息

- 编辑:仪器仪表WXF

- 声明:凡本网注明" 来源:仪商网"的所有作品,版权均属于仪商网,未经本网授权不得转载、摘编使用。

经本网授权使用,并注明"来源:仪商网"。违反上述声明者,本网将追究其相关法律责任。

本网转载并注明自其它来源的作品,归原版权所有人所有。目的在于传递更多信息,并不代表本网赞同其观点或证实其内容的真实性,不承担此类作品侵权行为的直接责任及连带责任。如有作品的内容、版权以及其它问题的,请在作品发表之日起一周内与本网联系,否则视为放弃相关权利。

本网转载自其它媒体或授权刊载,如有作品内容、版权以及其它问题的,请联系我们。相关合作、投稿、转载授权等事宜,请联系本网。

QQ:2268148259、3050252122。 -

-

示波器测量小信号波形干扰问题及解决之道电子行业|2025-04-07

示波器测量小信号波形干扰问题及解决之道电子行业|2025-04-07 -

鼎阳科技:为消费电子行业打造全方位测试解决方案电子行业|2025-04-02

鼎阳科技:为消费电子行业打造全方位测试解决方案电子行业|2025-04-02 -

【解决方案】精准贴片电感测试,专业仪器+夹具助力高效分析电子行业|2024-12-31

【解决方案】精准贴片电感测试,专业仪器+夹具助力高效分析电子行业|2024-12-31 -

仪器仪表解决方案:助力各行业精确测试与测量需求电子行业|2024-11-26

仪器仪表解决方案:助力各行业精确测试与测量需求电子行业|2024-11-26 -

【解决方案】高频变压器信赖之选,TH6XX系列实现绝缘电阻多脚位精确扫描电子行业|2024-11-26

【解决方案】高频变压器信赖之选,TH6XX系列实现绝缘电阻多脚位精确扫描电子行业|2024-11-26 -

自动化控制系统如何推动生产智能化,实现更高效的工业管理?电子行业|2025-01-22

自动化控制系统如何推动生产智能化,实现更高效的工业管理?电子行业|2025-01-22 -

学习使用Arduino Uno和OpenPLC构建光电传感器系统电子行业|2024-03-14

学习使用Arduino Uno和OpenPLC构建光电传感器系统电子行业|2024-03-14 -

实践ATX 3.0标准,为PC电源提供精准的测试解决方案电子行业|2023-10-31

实践ATX 3.0标准,为PC电源提供精准的测试解决方案电子行业|2023-10-31 -

ITECH电池强制放电的测试解决方案电子行业|2023-09-20

ITECH电池强制放电的测试解决方案电子行业|2023-09-20 -

锂电池生产厂房环境在线检测方案电子行业|2023-09-16

锂电池生产厂房环境在线检测方案电子行业|2023-09-16